2. 디지털 보호계전기 구조

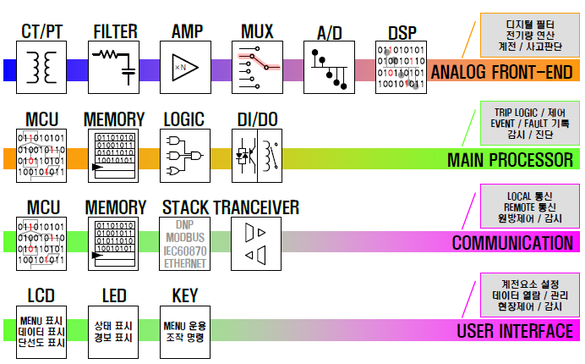

2.1 FUNCTIONAL BLOCK DIAGRAM (TYPICAL SCHEME)

2.2 ANALOG FRONT-END(1/4)

정의

- 주처리 MCU(또는 DSP)가 아날로그 신호를 디지털 DOMAIN에서 연산/처리할 수 있도록 전처리를 담당하는 기능 회로/MODULE

기능 (1/2)

- 계전기 외부와의 신호절연 : 변성기를 이용하여 자기회로로 신호 전달

- 계통의 고전압/대전류를 ±15V 및 5V 이하의 회로에서 처리할 수 있는 수준으로 변환

- CT(5A 또는 1A / 5mA≥), IoCT(1.5mA / 1.0mA≥), PT(110V 또는 63.5V / 5V≥)

- 계통의 왜란 및 고조파 유입 억제

- 노이즈로부터 내부회로를 보호하고 오동작을 방지

- 노이즈 대책 : VARISTOR, CAPACITOR, F.G ROUTE, COIL, FERRITE CORE FILTER

- 고조파 대책 : 저역통과필터 (BUTTERWORTH, CHEBYSHEV, BESSEL,…)

- 아날로그 신호를 디지털 신호로 변환

- A/D 방식 : SAR, Δ-Σ, FLASH

2.2 ANALOG FRONT-END(2/4)

기능 (2/2)

디지털 필터에 의한 기본파 Phasor 추출

- A/D 샘플 취득 단계 : 노이즈 샘플 제거, 위상 지연 보상, GAIN 보상,…

- Phasor 추출 단계 : 고조파 제거, DC OFFSET 제거,…

고정밀 계측연산

- TRUE RMS 연산 : 전압, 전류, 전력, 주파수,…

- HARMONICS 연산 : 2 ~ Nth 고조파 (N은 제품 사양에 따라 다름)

보호 계전 알고리즘 수행

- 50/51P(OCR, Over Current Relay), 50/51N(OCGR, Over Current Ground),

67(DOCR, Directional OCR), 46(NSOCR, Negative Sequence OCR), 49(Thermal),

27(UVR, Under Voltage), 59(OVR, Over Voltage), 47(NSOVR, Negative Sequence), 32(Dirctional Power) 등

- 각 계전요소 별 독립된 PICK-UP 상태 출력 (TRIP-LOGIC에 적용)

DISTURBANCE RECORD (EVENT TRIGGERED WAVE RECORD)

- 설정된 EVENT발생시 일정시간 동안 모든 아날로그 입력과 DI/DO의 파형을 기록

- 기록된 파형을 COMTRADE FORMAT으로 변환/저장 후 별도 장비를 통한 재현

2.2 ANALOG FRONT-END (3/4)

사양 (1/2)

20In(In은 5A기준) 이상에서 왜곡없이 신호처리할 수 있을 것 (한전사양은 40In)

- 한전 : CT 과전류정수(20In) × DC offset은 과전류정수의 200% = 40In

- OP AMP, MUX, A/D 등 아날로그 부품의 최대 입출력 SPAN을 고려한 설계 필요

- 저전류에서의 경제적인 디지털 정밀도 확보 방안 필요 : PGA, MULTI-A/D

2Vn(Vn은 110V기준) 이상에서 왜곡없이 신호처리할 수 있을 것

- 저압계통 : 380, 440V 계통에서 계전기가 외부 PT없이 직결될 경우는 별도

급격한 전압, 전류 순시치 변화에 대한 추종능력이 뛰어날 것

- OP AMP SLEW RATE : 처리하고자 하는 고조파 차수에 따라 다름

- A/D 변환 방식 : Δ-Σ방식은 느린 응답특성으로 계전기 적용이 어려움

-10℃~50℃의 온도범위와 상대습도 80%의 환경에서 오차기준(5%이하)을 만족할 것

- KEMC1120 기준

- 아날로그 부품 선정시 온도/습도 변화에 대한 오차 변화율 검토(PPM단위)

- 운전시 부품의 온도상승에 의한 경년변화 성능을 고려할 것

2.2 ANALOG FRONT-END (4/4)

사양 (2/2)

위상지연 및 연산지연을 최소화할 것

- 전류 크기에 따른 CT의 위상 SHIFT 고려 : 전력계측 오차 유발

- 디지털 필터에서의 시지연 최소화 : RDFT, HDFT, SDFT, COSINE FILTER,…

입력부담이 작을 것

- 최대 단락 및 지락 사고시 CT포화 방지

- 외부 CT 및 PT의 가격 절감 효과

아날로그 신호처리 회로와 부품의 자기진단

- 부품의 파손/오동작시 계전기 오동작/오부동작 방지

외부 노이즈 내성 및 서지 강도가 높을 것

- 개폐서지, 뇌서지, 정전기 및 비선형부하에 의한 고조파 등의 현장 왜란에 대해

최소한의 성능기준을 규격화 : KEMC1120, IEC60255, IEC61000,…

- 5장 “디지털 보호계전기 관련규격”

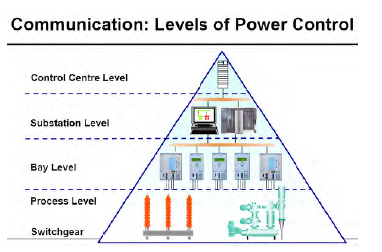

2.3 COMMUNICATION (1/1)

정의

PC 또는 WORKSTATION 기반의 감시반에서 계전요소의 정정치와 CT/PT비율, TRIP LOGIC 및 각종 부가요소의 적절한 설정을 DOWNLOAD하여 피 보호 계통이 안정적으로 운영되도록 하고 보호계전기의 동작상태, 운전이력, 사고이력 등을 UPLOAD하여 계통의 운영 상황을 감시하고 그 상황에 따른 적절한 조치를 자동 또는 수동으로 하도록 하며 고장을 포함한 이상상태를 분석하여 신속한 복구를 할 수 있도록 지원하는 시스템 연계용 기능 MODULE (4장 “PC 운영 프로그램 및 원격통신 기능”)

정의

- 주처리 MCU(또는 DSP)가 아날로그 신호를 디지털 DOMAIN에서 연산/처리할 수 있도록 전처리를 담당하는 기능 회로/MODULE

기능 (1/2)

- 계전기 외부와의 신호절연 : 변성기를 이용하여 자기회로로 신호 전달

- 계통의 고전압/대전류를 ±15V 및 5V 이하의 회로에서 처리할 수 있는 수준으로 변환

- CT(5A 또는 1A / 5mA≥), IoCT(1.5mA / 1.0mA≥), PT(110V 또는 63.5V / 5V≥)

- 계통의 왜란 및 고조파 유입 억제

- 노이즈로부터 내부회로를 보호하고 오동작을 방지

- 노이즈 대책 : VARISTOR, CAPACITOR, F.G ROUTE, COIL, FERRITE CORE FILTER

- 고조파 대책 : 저역통과필터 (BUTTERWORTH, CHEBYSHEV, BESSEL,…)

- 아날로그 신호를 디지털 신호로 변환

- A/D 방식 : SAR, Δ-Σ, FLASH

2.2 ANALOG FRONT-END(2/4)

기능 (2/2)

디지털 필터에 의한 기본파 Phasor 추출

- A/D 샘플 취득 단계 : 노이즈 샘플 제거, 위상 지연 보상, GAIN 보상,…

- Phasor 추출 단계 : 고조파 제거, DC OFFSET 제거,…

고정밀 계측연산

- TRUE RMS 연산 : 전압, 전류, 전력, 주파수,…

- HARMONICS 연산 : 2 ~ Nth 고조파 (N은 제품 사양에 따라 다름)

보호 계전 알고리즘 수행

- 50/51P(OCR, Over Current Relay), 50/51N(OCGR, Over Current Ground),

67(DOCR, Directional OCR), 46(NSOCR, Negative Sequence OCR), 49(Thermal),

27(UVR, Under Voltage), 59(OVR, Over Voltage), 47(NSOVR, Negative Sequence), 32(Dirctional Power) 등

- 각 계전요소 별 독립된 PICK-UP 상태 출력 (TRIP-LOGIC에 적용)

DISTURBANCE RECORD (EVENT TRIGGERED WAVE RECORD)

- 설정된 EVENT발생시 일정시간 동안 모든 아날로그 입력과 DI/DO의 파형을 기록

- 기록된 파형을 COMTRADE FORMAT으로 변환/저장 후 별도 장비를 통한 재현

2.2 ANALOG FRONT-END (3/4)

사양 (1/2)

20In(In은 5A기준) 이상에서 왜곡없이 신호처리할 수 있을 것 (한전사양은 40In)

- 한전 : CT 과전류정수(20In) × DC offset은 과전류정수의 200% = 40In

- OP AMP, MUX, A/D 등 아날로그 부품의 최대 입출력 SPAN을 고려한 설계 필요

- 저전류에서의 경제적인 디지털 정밀도 확보 방안 필요 : PGA, MULTI-A/D

2Vn(Vn은 110V기준) 이상에서 왜곡없이 신호처리할 수 있을 것

- 저압계통 : 380, 440V 계통에서 계전기가 외부 PT없이 직결될 경우는 별도

급격한 전압, 전류 순시치 변화에 대한 추종능력이 뛰어날 것

- OP AMP SLEW RATE : 처리하고자 하는 고조파 차수에 따라 다름

- A/D 변환 방식 : Δ-Σ방식은 느린 응답특성으로 계전기 적용이 어려움

-10℃~50℃의 온도범위와 상대습도 80%의 환경에서 오차기준(5%이하)을 만족할 것

- KEMC1120 기준

- 아날로그 부품 선정시 온도/습도 변화에 대한 오차 변화율 검토(PPM단위)

- 운전시 부품의 온도상승에 의한 경년변화 성능을 고려할 것

2.2 ANALOG FRONT-END (4/4)

사양 (2/2)

위상지연 및 연산지연을 최소화할 것

- 전류 크기에 따른 CT의 위상 SHIFT 고려 : 전력계측 오차 유발

- 디지털 필터에서의 시지연 최소화 : RDFT, HDFT, SDFT, COSINE FILTER,…

입력부담이 작을 것

- 최대 단락 및 지락 사고시 CT포화 방지

- 외부 CT 및 PT의 가격 절감 효과

아날로그 신호처리 회로와 부품의 자기진단

- 부품의 파손/오동작시 계전기 오동작/오부동작 방지

외부 노이즈 내성 및 서지 강도가 높을 것

- 개폐서지, 뇌서지, 정전기 및 비선형부하에 의한 고조파 등의 현장 왜란에 대해

최소한의 성능기준을 규격화 : KEMC1120, IEC60255, IEC61000,…

- 5장 “디지털 보호계전기 관련규격”

2.3 COMMUNICATION (1/1)

정의

PC 또는 WORKSTATION 기반의 감시반에서 계전요소의 정정치와 CT/PT비율, TRIP LOGIC 및 각종 부가요소의 적절한 설정을 DOWNLOAD하여 피 보호 계통이 안정적으로 운영되도록 하고 보호계전기의 동작상태, 운전이력, 사고이력 등을 UPLOAD하여 계통의 운영 상황을 감시하고 그 상황에 따른 적절한 조치를 자동 또는 수동으로 하도록 하며 고장을 포함한 이상상태를 분석하여 신속한 복구를 할 수 있도록 지원하는 시스템 연계용 기능 MODULE (4장 “PC 운영 프로그램 및 원격통신 기능”)

2.4 USER INTERFACE (1/2)

정의

- 사용자가 보호 계전기 전면의 KEY, LED, LCD 등의 입출력 장치를 이용하여 MENU운용,

조작, DATA 열람, 관리, 제어, 감시 등의 작업을 할 수 있도록 구현된 기능 MODULE

기능 (1/2)

MENU

- 보호 계전기에서 제공하는 모든 항목들을 기능별로 분류하여 표시하고 KEY나 JOG SHUTTLE 등의 입력 장치로 선택 조작 할 수 있 어야 함

표시

- 계측값, 단선도, 감시 상태, 경보, 계전요소 정정값, 운전이력, 사고이력, 부가기능 설정값

2.5 USER INTERFACE (2/2)

기능 (2/2)

데이터 관리

- 운전/고장이력 DOWNLOAD 및 삭제

설정변경

- 계전요소 정정 변경

- 부가기능 설정 변경

제어

- 차단기 제어

- 접점 제어

요구사양

- 실시간성이 높을 것

- 표시형태나 방법이 직관적이어서 사용자 오해에 의한 오조작, 오동작이 없을 것

- 외부인 또는 오조작에 대한 보안성이 높을 것 : PASSWORD, LOCK-KEY

- 온습도에 대한 영향이 없을 것

정의

- 사용자가 보호 계전기 전면의 KEY, LED, LCD 등의 입출력 장치를 이용하여 MENU운용,

조작, DATA 열람, 관리, 제어, 감시 등의 작업을 할 수 있도록 구현된 기능 MODULE

기능 (1/2)

MENU

- 보호 계전기에서 제공하는 모든 항목들을 기능별로 분류하여 표시하고 KEY나 JOG SHUTTLE 등의 입력 장치로 선택 조작 할 수 있 어야 함

표시

- 계측값, 단선도, 감시 상태, 경보, 계전요소 정정값, 운전이력, 사고이력, 부가기능 설정값

2.5 USER INTERFACE (2/2)

기능 (2/2)

데이터 관리

- 운전/고장이력 DOWNLOAD 및 삭제

설정변경

- 계전요소 정정 변경

- 부가기능 설정 변경

제어

- 차단기 제어

- 접점 제어

요구사양

- 실시간성이 높을 것

- 표시형태나 방법이 직관적이어서 사용자 오해에 의한 오조작, 오동작이 없을 것

- 외부인 또는 오조작에 대한 보안성이 높을 것 : PASSWORD, LOCK-KEY

- 온습도에 대한 영향이 없을 것